9月2日消息,日本在半导体材料方面居于世界领先地位,但因为缺乏完整产业链,工艺制程方面一直默默无闻,不过近些年,在日本政府大力扶持下,日本开始在工艺制程方面发力。

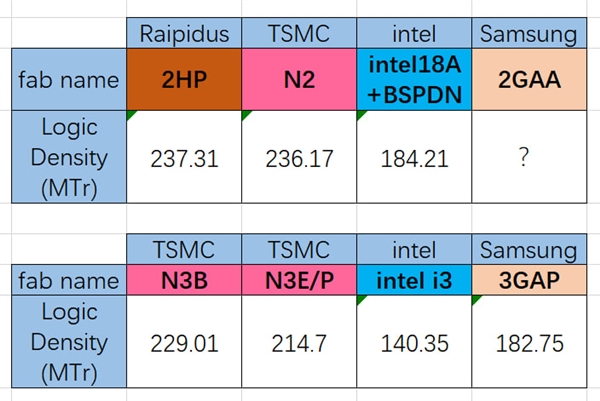

日本初创晶圆代工企业Rapidus最近公布了其2HP 2nm工艺的逻辑密度指标,竟然超越了台积电N2,并且远远优于Intel 18A,令人惊讶。

据悉,Rapidus 2HP的逻辑晶体管密度为每平方毫米2.3731亿个,略微高于台积电N2 2.3617亿个,幅度不到0.5%,卡得非常准。

Intel 18A的晶体管密度没有官方数据,估计约为每平方毫米1.8421亿个,日本比之胜出接近30%!

至于台积电N3B/E/P、Intel 3、三星3GAP等一系列3nm工艺,更是望尘莫及。

另外,Rapidus 2HP的单元库包括一个HD高密度库,高度为138个单元,间距为G45。

不过令人存疑的是,权威半导体分析机构TechInsights此前分析认为,在高密度的逻辑晶体管密度指标上,台积电N2其实做到了每平方毫米3.13亿个,Intel 18A也有2.38亿个,甚至三星2GAA都不算差约为2.31亿个。

这些数据,远高于日本方面宣传的。

另外需要指出的是,Intel 18A晶体管密度明显低于台积电N2,并不代表其水平更差,而是采用了新的背面供电技术,占据了一些前方金属层,导致逻辑密度偏低。

同时,Intel主要追求的不是最大密度,而是最高能效。

总的来说,如果Rapidus公布的数据属实,至少说明日本2nm工艺达到了相当高的水准,但超越台积电、Intel还有待商榷,尤其是这是一家新兴企业。

Rapidus 2HP PDK(工艺设计包)将于2026年一季度提供,计划2027年投入量产,但用于什么芯片尚不清楚。

当然,就算造假了也没啥,鞠个躬的事儿嘛!

|